Unlock The Future Master Fpga Hls Programming Tech Shorts Fpga

Unlock The Future Master Fpga Hls Programming Tech Shorts Fpga About press copyright contact us creators advertise developers terms privacy policy & safety how works test new features nfl sunday ticket press copyright. Smarthls™ training session 1: image processing on the polarfire® video kit. training2. smarthls™ training session 2: multi threaded digit recognition on the polarfire® video kit. training3. smarthls™ training session 3: axi interfaces to ddr & mi v soft processor on the polarfire® video kit. training4. smarthls™ training session 4.

Parallel Programming For Fpgas Kastner Research Group These are examples used in the tutorial productive parallel programming on fpga with high level synthesis, given at ppopp'18, sc'18, sc'19, hipeac'20, sc'20, isc'21, and sc'21. for comprehensive coverage of hls transformations for hpc, we refer to our work transformations of high level synthesis codes for high performance computing , available. The fpga design journey commences with high level synthesis (hls), a pivotal phase where the engineer articulates the intended functionality using high level languages like c, c , or systemc. Here was the story of my personal experience. to grab a computation intensive algorithm you're familiar with or interested, exploring how to apply hls to make it work. analysis of various hls pragma in terms of throughout and latency. finally, to buy a pynq board for some experiments. then, publishing the work. or share to someone are new to. You cannot take an arbitrary piece of c code, drop it in to an hls compiler, and expect any kind of sensible result (or even a result at all). hls is great, but make sure you keep track of the structure of the generated hardware. for loops are fine in hdl, too, so long as you know what you are implying by them.

Open Source Tools Help Simplify Fpga Programming Embedded Here was the story of my personal experience. to grab a computation intensive algorithm you're familiar with or interested, exploring how to apply hls to make it work. analysis of various hls pragma in terms of throughout and latency. finally, to buy a pynq board for some experiments. then, publishing the work. or share to someone are new to. You cannot take an arbitrary piece of c code, drop it in to an hls compiler, and expect any kind of sensible result (or even a result at all). hls is great, but make sure you keep track of the structure of the generated hardware. for loops are fine in hdl, too, so long as you know what you are implying by them. In this context, it is timely to take a holistic view of the recent developments in the field of fpga hls. there have been several prior efforts that survey a comprehensive set of existing fpga hls tools, the associated programming models, as well as the underlying synthesis and optimization techniques [45, 46, 47, 48]. Silexica’s slx fpga tool, based on over 10 years of compiler technology research, provides practical solutions to the challenges discussed in this article by addressing these challenges through each step of the hls design process. first, slx fpga analyzes the c c source code for synthesizability and provides automatic and guided code.

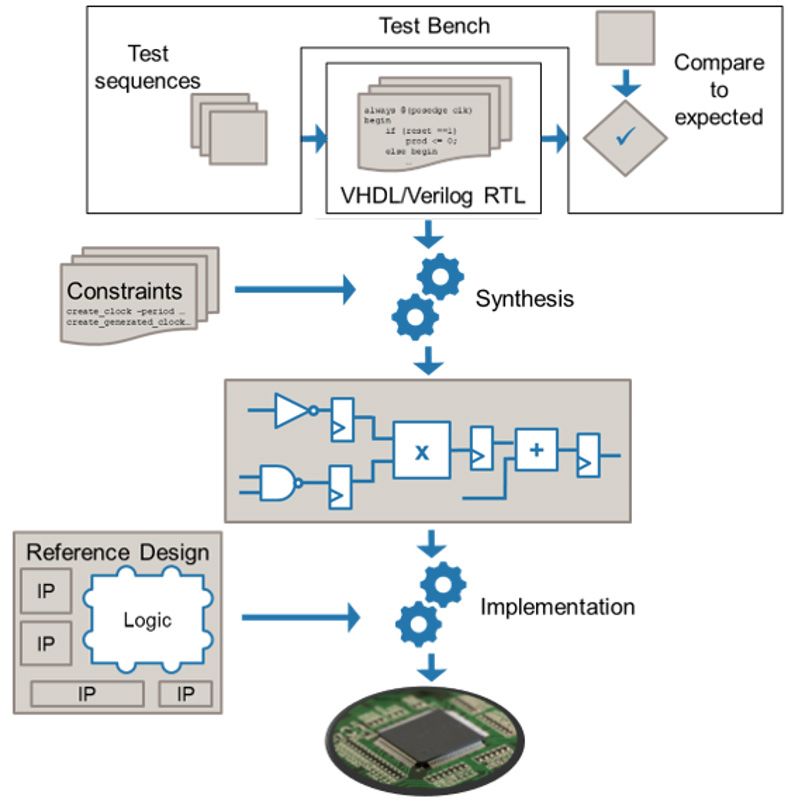

Fpga Programming Matlab Simulink In this context, it is timely to take a holistic view of the recent developments in the field of fpga hls. there have been several prior efforts that survey a comprehensive set of existing fpga hls tools, the associated programming models, as well as the underlying synthesis and optimization techniques [45, 46, 47, 48]. Silexica’s slx fpga tool, based on over 10 years of compiler technology research, provides practical solutions to the challenges discussed in this article by addressing these challenges through each step of the hls design process. first, slx fpga analyzes the c c source code for synthesizability and provides automatic and guided code.

Optimizing An Fpga Hls Design With Fpga Tool Settings Plunify Blog

Comments are closed.