Pcie Root Port Projects Rocketboards Org

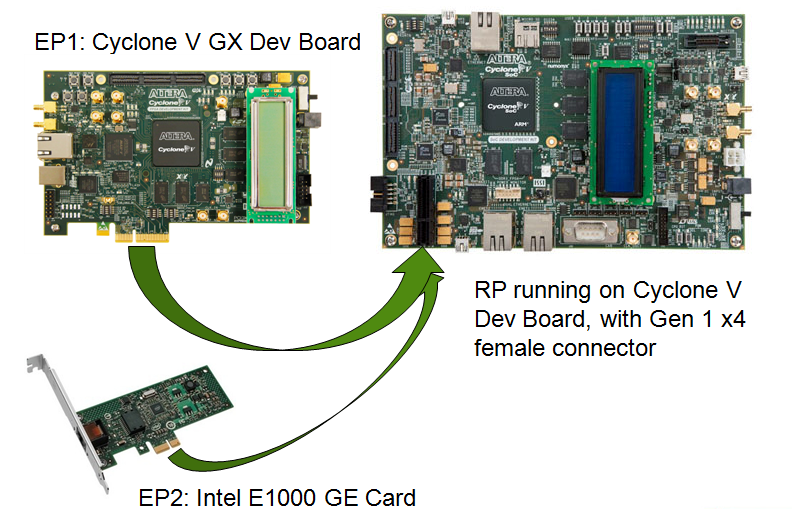

Pcie Root Port Projects Rocketboards Org Lftan, rockethwong. please refer to this project for updated pcie example design with msi support. this example shows functionality of the hip pcie root port with hps (arm) as the host processor. it shows the entire design flow from qsys quartus ii to device tree handoff to linux application access. there are two hardware configurations. The fpga design is based on the golden system reference design (gsrd). newly added modules include: pcie rootport (rp) ip, msi togic generator ip, msgdma and throughput measurement modules. the design demonstrates the altera pcie hip root port ability to enumerate a gen1x4 pcie endpoint and measure the link throughput.

Arria 10 Arria V Cyclone V Pcie Root Port With Msi Projects A pcie root port subsystem and 256kb on chip ram have been added. please refer to the qsys files included with the root port hardware design (listed in the build stratix 10 pcie root port and integrating u boot fsbl section below) for further detail. a few more components, such as performance counter and jtag avalon masters, have been added to. Pcie root port. an example which implements a non msi pcie root port on an altera soc development board (linked at the top of the project page, http. Rocketboards general. akochubey july 10, 2020, 11:08am 1. hi all, we are developing cyclone v soc based board, which will make use of 2 pcie root ports (each having dedicated sata controller on another end). so far, we are investigating “pcie root port” example (simple one, without sgdma) and have some general questions about it. Hi all, i had a question about this reference design. i am kind of confused. it seems like the entire reference design is done for arria10 device 10as066n3f40e2sge2 but the arria 10 soc development kit has 10as066n3f40i2sges. it is also mentioned in the arria 10 soc development kit user’s guide(link for user guide given in arria10 pcie rootport with msi page) that the device on the board is.

Stratix 10 Pcie Root Port With Msi Projects Rocketboards Org Rocketboards general. akochubey july 10, 2020, 11:08am 1. hi all, we are developing cyclone v soc based board, which will make use of 2 pcie root ports (each having dedicated sata controller on another end). so far, we are investigating “pcie root port” example (simple one, without sgdma) and have some general questions about it. Hi all, i had a question about this reference design. i am kind of confused. it seems like the entire reference design is done for arria10 device 10as066n3f40e2sge2 but the arria 10 soc development kit has 10as066n3f40i2sges. it is also mentioned in the arria 10 soc development kit user’s guide(link for user guide given in arria10 pcie rootport with msi page) that the device on the board is. Build arria 10 pcie root port . download the project: the project is available here: a10 pcie soc devkit.tar.gz. build the project: the root port design is based on the arria 10 ghrd. follow the instructions listed at compiling hardware design, but replace the ghrd source code file a10 soc devkit ghrd.tar.gz with the file listed above. The avalon master port of the pcie core must be connected to the memory through a address expanded and the window this provides to the ram can be set in power of two increments so 1gb, 2 gb or 4gb. in our case we had our boot loader configured to give the linux kernel 3gb of memory, and the pcie core had a 2gb window to the ram.

Stratix 10 Pcie Root Port With Msi Projects Rocketboards Org Build arria 10 pcie root port . download the project: the project is available here: a10 pcie soc devkit.tar.gz. build the project: the root port design is based on the arria 10 ghrd. follow the instructions listed at compiling hardware design, but replace the ghrd source code file a10 soc devkit ghrd.tar.gz with the file listed above. The avalon master port of the pcie core must be connected to the memory through a address expanded and the window this provides to the ram can be set in power of two increments so 1gb, 2 gb or 4gb. in our case we had our boot loader configured to give the linux kernel 3gb of memory, and the pcie core had a 2gb window to the ram.

Comments are closed.